Link шины pci express

Эмблема PCI Conventional

Вот уже более десяти лет PCI – шина для подключения периферийных устройств к материнской плате компьютера – находится внутри практически каждого компьютера и, даже несмотря на моральное устаревание и уже недостаточную пропускную способность, продолжает (пока ещё) оставаться основной шиной для подключения к системе внешних устройств. Тем не менее она неуклонно сдаёт позиции новой последовательной шине PCI-Express, о которой чуть ниже.

В далёком 1991 году компания Intel представила первую спецификацию системной шины PCI – Peripheral Component Interconnect (дословно: взаимосвязь периферийных компонентов ). А в 1993 году уже началось активное продвижение на рынок шины PCI 2.0, которая дала толчок увеличению числа ориентированных на неё продуктов и довольно быстро вытеснила изрядно устаревшие к тому времени шины ISA и EISA.

Причины успеха PCI – это гораздо большая скорость и возможность динамического конфигурирования периферийных устройств, подключённых к PCI (чего не было в ISA), то есть распределения ресурсов между периферийными устройствами наиболее приемлемым в данный момент времени образом и без постороннего вмешательства.

Основные тактико-технические характеристики PCI 2.0:

- частота шины – 33,33 МГц, передача синхронная

- разрядность шины – 32 бит

- пиковая пропускная способность – 133 Мбит/с

- адресное пространство памяти – 32 бит (4 Гбайт)

- адресное пространство портов ввода-вывода – 32 бит (4 Гбайт)

- количество подключаемых устройств – до четырёх (для увеличения их количества используется мост PCI-to-PCI)

- конфигурационное адресное пространство (для одной функции) 256 байт

- напряжение 3,3 или 5 В

Вскоре PCI «взяли на вооружение» также платформы с процессорами Alpha, MIPS, PowerPC, SPARC и другие.

Ещё большее распространение получил стандарт 2.2.

- возможность одновременной работы нескольких устройств bus-master (так называемый конкурентный режим)

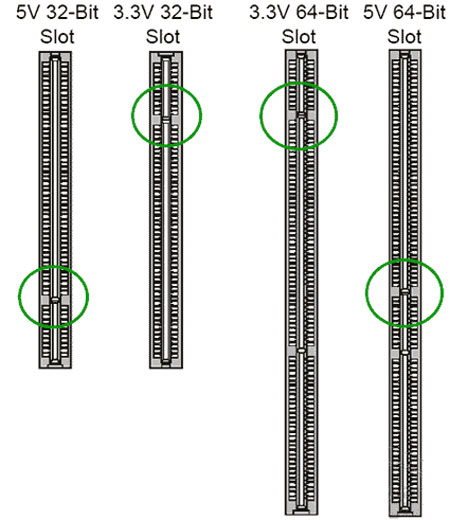

- появление универсальных карт расширения, способных работать как в слотах 5 В, так и в 3,3 В

- появились расширения PCI66 и PCI64 (ширина шины может быть увеличена до 64 бит, а также допускается разгон тактовой частоты до 66 МГц – вдвое по сравнению с PCI 2.0)

- сделанные в соответствии с этими стандартами карты расширения имеют универсальный разъём и способны работать практически во всех более поздних разновидностях слотов шины PCI, а также, в некоторых случаях, и в слотах 2.1

Со времён анонса PCI 2.0 разработкой и продвижением стандарта занимается специальная организация – консорциум PCI-SIG (Special Interest Group), она же занимается продвижением PCI Express.

Существует множество вариаций на тему PCI 2.Х, наиболее распространённые из которых:

- AGP – разработана на базе PCI 2.1 и предназначена для использования с графическими адаптерами, характеризуется отсутствием арбитража интерфейса, то есть допускается подключение к этой шине только одного устройства, также устранена мультиплексированность

- PCI-X – ускоренная до 133 МГц (также выпускались варианты с 266 и 533 МГц) шина PCI 2.2 с обязательно 64-битной разрядностью интерфейса

- Compact-PCI – системная шина, широко используемая в промышленной автоматике. Электрически шина соответствует обычной PCI и обычно использует тот же набор микросхем, но физически разъём выполнен по-другому, что позволяет использовать «горячее» подключение плат

- mini-PCI – применяется в портативных компьютерах

- Card Bus (32-разрядная версия стандарта PCMCIA, допускающая «горячее» подключение)

Сводная таблица конструктивов карт и слотов в зависимости от версии стандарта

| Стандарт | Макс. Скорость, Мб/с | Тип слота | Тип карты |

|---|---|---|---|

| PCI 1.x-2.0 | 133 | 32 бит, 5 В | 32 бит, 5 В |

| PCI 2.1-2.3 33 MГц | 133 | 32 бит, 5 В | 32 бит, 5 В / универсальный |

| PCI 2.2-2.3 66 MГц | 266 | 32 бит, 3,3 В | 32 бит, 3,3 В / универсальный |

| PCI64 33 МГц (v 2.1) | 266 | 64 бит, 5 В | 64 бит, 5 В / универсальный |

| PCI64 33 МГц (v 2.2) | 266 | 64 бит, 3,3 В | 64 бит, 3,3 В / универсальный |

| PCI64 66 МГц | 533 | 64 бит, 3,3 В | 64 бит, 3,3 В / универсальный |

| PCI-X 1.0 | 1024 | 64 бит, 3,3 В | 64 бит, 3,3 В / универсальный |

| PCI-X 1.0 | 4096 | 64 бит, 3,3 В | 64 бит, 3,3 В |

Однако, как и многие параллельные шинные решения (те же Parallel ATA, SCSI), шина PCI в данное время находится на границе разумного масштабирования производительности, после которого «гонка частот и разрядности» приведёт к непозволительно высоким технологическим усложнениям и, соответственно, к затратам. Но на данный момент проблема эффективной масштабируемости и наращивания уже решена, ведь в компьютерной индустрии уже полным ходом идёт переезд с PCI на новую последовательную шину PCI-Express.

Различия топологий PCI и PCI-Express

PCI-Express

Разработка рабочей группой Arapahoe, основанной компаниями Compaq, Dell, IBM, Intel и Microsoft при участии организации PCI-SIG, нового межкомпонентного интерфейса была начата фирмой Intel еще тогда, когда только ожидался выход в свет AGP 3.0 (он же AGP 8х). Так, программную модель PCI планировали унаследовать и в новом интерфейсе, чтобы системы и контроллеры могли быть доработаны для использования новой шины путём замены только физического уровня, без доработки программного обеспечения. Сам же интерфейс должен был быть последовательным. Это означало, во-первых, однозначное подключение «точка-точка», исключающее арбитраж шины и перетасовку ресурсов (как частный случай – прерываний). Во-вторых, упрощалась схемотехника, разводка и монтаж. В-третьих, экономилось место.

Анонс первой базовой спецификации PCI-Express состоялся в июле 2002 года, когда уже стало ясно, что PCI-Express – это последовательный интерфейс, нацеленный на использование в качестве локальной шины и имеющий много общего с сетевой организацией обмена данными, в частности, топологию типа «звезда» и стек протоколов.

Для взаимодействия с остальными узлами ПК, которые так или иначе обходятся собственными шинами, основной связующий компонент системной платы – Root Complex Hub (узел, являющийся перекрёстком процессорной шины, шины памяти и PCI-Express) – предусматривает систему мостов и свитчей. Логика всей структуры такова, что любые межкомпонентные соединения непременно оказываются построенными по принципу «точка-точка», свитчи-коммутаторы выполняют однозначную маршрутизацию пакета от отправителя к получателю.

Соединение между двумя устройствами PCI Express называется link и состоит из одного (называемого 1x) или нескольких (2x, 4x, 8x, 12x, 16x и 32x) двунаправленных последовательных соединений lane . Каждое устройство должно поддерживать соединение 1x.

| Число линий PCI Express lane count) | Пропускная способность соединения (link) в одном направлении | Суммарная пропускная способность соединения (link) |

|---|---|---|

| 1 | 250 Мбайт/с | 500 Мбайт/с |

| 2 | 500 Мбайт/с | 1 Гбайт/с |

| 4 | 1 Гбайт/с | 2 Гбайт/с |

| 8 | 2 Гбайт/с | 4 Гбайт/с |

| 16 | 4 Гбайт/с | 8 Гбайт/с |

| 32 | 8 Гбайт/с | 16 Гбайт/с |

Таблица. Пропускная способность шины PCI Express с разным количеством связей

В спецификации PCI-Express 2.0 планируется увеличить пропускную способность lane до 5 Гбит/с при сохранении совместимости с PCI-Express 1.1.

Использование шин и устройств PCI Express.

Шины ( links ) PCI Express показаны оранжевым цветом

Кроме всего прочего, PCI Express предлагает:

- стек протоколов, каждый уровень которого может быть усовершенствован, упрощён или заменён, не влияя на остальные. Например: может быть использован иной носитель сигнала – или может быть упразднена маршрутизация в случае выделенного канала только для одного устройства (как в случае PCI Express x16 для графики)

- возможности «горячей» замены карт (заложены в спецификации, опционально реализуются в серверных системах)

- возможности создания виртуальных каналов, гарантирования пропускной полосы и времени отклика, сбора статистики QoS (Quality of Service – качество обслуживания) 8

- возможности контроля целостности передаваемых данных (CRC) 8

- поддержка технологий энергосбережения (ACPI) 8

Итоги

Как мы видим, последовательные интерфейсы пришли в компьютерную индустрию всерьёз и надолго. Не за горами времена, когда такие почётные долгожители, как PCI, IDE(PATA), SCSI, совсем уйдут со сцены, ибо преемники – PCI Express, Serial ATA, Serial Attached SCSI – уже агрессивно отвоёвывают позиции у «старичков». В стане процессорных шин пока паритет – архитектура K8 компании AMD c организацией процессорной шины на основе HyperTransport уже зарекомендовала себя как удачное решение, но и компания Intel с «последней редакцией» параллельной шины FSB (QPB) чувствует себя довольно уверенно и не собирается от неё отказываться.

Что касается возможной войны технологий PCI Express и HyperTransport, то здесь не тот случай – уж слишком разные сферы применения уготованы разработчиками этим решениям. Для вторжения в сферу сверхбыстрых передач у PCI Express недостаточно пропускной способности (максимум 8 ГБ/с для х16 против 41 ГБ/с у HyperTransport). Что касается работы HyperTransport с периферийными контроллерами, то данная шина не обладает для этого достаточными возможностями протоколов в силу своего изначального предназначения – замены процессорной шины, первое упоминание о «горячем» подключении появилось лишь в спецификации HyperTransport 3.0, да и стандартом пока что не предусмотрено внешних разъёмов.

Новый стандарт на базе PCIe 5.0 «свяжет» CPU и GPU — что о нем известно

Консорциум CXL представил новый открытый стандарт — Compute Express Link (CXL). Он поможет организовать высокоскоростную связь между процессором и другими устройствами — GPU, FPGA и памятью. В основу CXL 1.0 лег интерфейс PCIe 5.0, спецификация которого ожидается в этом году. Поговорим о технических подробностях и аналогах решения.

Зачем потребовался новый стандарт

Потребность в обработке и шифровании больших объемов данных, развитие систем ИИ и алгоритмов МО привели к росту популярности гетерогенных решений. В них процессоры общего назначения работают вместе с ускорителями — графическими процессорами, FPGA и микросхемами ASIC. Каждый компонент специализируется на выполнении конкретной задачи, что повышает производительность системы.

При обработке больших объемов данных (например, в дата-центрах), каналы для обмена информацией между гетерогенными компонентами порой становятся «бутылочным горлышком». Чтобы свести задержки к минимуму, консорциум CXL (в который входят облачные провайдеры и разработчики оборудования для ЦОД) представил стандарт Compute Express Link.

Что известно о стандарте

Он основан на интерфейсе PCI Express 5.0, предназначенном для подключения серверных компонентов. Это означает, что стандарт будет поддерживать пропускную способность между вычислительными элементами до 128 Гбайт/с на 16 линиях. При этом будет использоваться экономное кодирование 128b/130b, реализованное еще в PCI Express 3.0.

Схематически подключение можно изобразить следующим образом:

CXL имеет три метода интерфейса. Первый — режим ввода-вывода для передачи команд и обновления статусов устройств. Второй — протокол памяти для разделения RAM между хостом и ускорителем. Третий — интерфейс, который обеспечит когерентность памяти.

О чем мы пишем в корпоративном блоге:

Потенциал и недостатки

Шина PCIe 5.0 специально разработана для решения задач, которые требуют максимальной пропускной способности — работы с графическими процессорами, сетевыми технологиями, высоконагруженными системами. Поэтому разработчики CXL ожидают, что новый стандарт будет пользоваться спросом у институтов, занимающихся машинным обучением, и операторов дата-центров. Поскольку технология «заточена» под GPU, FPGA, ASIC и другие ускорители, в архитектуре пользовательских ПК она, скорее всего, применяться не будет.

В ИТ-сообществе есть мнение, что новый стандарт может не получить широкого распространения. Так как в отрасли и так достаточно аналогичных стандартов и спецификаций, например CCIX и GenZ (о них мы поговорим ниже). Широкой адаптации стандарта может помешать модель его распространения. Хотя Compute Express Link и является открытым стандартом, доступ к его полной спецификации имеют только члены консорциума. И пока непонятно, будут ли они конкурировать друг с другом на рынке после релиза.

/ Wikimedia / BiomedNMR / CC BY-SA

Похожие стандарты

Как мы упоминали выше, у CXL есть несколько аналогов, среди которых GenZ и CCIX.

Спецификация шины GenZ, которую называют «возможным преемником PCIe», вышла в феврале 2018. В ее разработке приняли участие около пятидесяти крупных ИТ-компаний. Цель создания стандарта не отличается от целей CXL — повысить скорость обмена данными между процессором, памятью и графическими картами.

Представители консорциума утверждают, что Gen-Z обходит ограничение связи точка-точка, которое присутствует в PCIe, и обращается к памяти напрямую. Спецификация уже готова и лежит в открытом доступе на сайте консорциума.

CCIX — еще один консорциум, в составе которого числятся именитые корпорации. Первая спецификация одноименного стандарта вышла летом 2018. Она основана на PCIe 4.0, что позволяет добиться пропускной способности в 25 Гбайт/с.

Концепцию архитектуры на базе первой спецификации CCIX уже реализовала компания Xilinx в своем чипе Versal на FPGA. В ближайшее время CCIX планируют внедрить и другие игроки рынка, некоторые из них уже представили тестовые реализации.

Будущее стандарта

Как минимум два консорциума уже опережают CXL по скорости разработки спецификаций. Однако есть шанс, что достоинства стандарта PCIe 5.0 помогут CXL опередить конкурентов и стать отраслевым стандартом для производителей процессоров и гетерогенных систем. Устройства на базе этой технологии помогут ускорить работу с данными в ЦОД и облаке, найдут применение в области разработки систем ИИ и HPC-решений.

Что еще почитать в нашем блоге на Хабре:

Источник